——当AI芯片遇见HPC仿真:JAX+XLA重构计算范式的可能性与边界

Google TPU(Tensor Processing Unit)自2015年问世以来,始终被视为深度学习加速的专用芯片。但在2024年,随着JAX框架的成熟和XLA编译器的泛化,TPU正悄然突破AI边界,向传统HPC仿真领域渗透。本文从架构、工具链、算法适配三维度,剖析TPU在仿真计算中的可行性、实现路径与适用场景。

一、TPU架构:为矩阵运算而生的”非冯·诺依曼”机器

1.1 核心硬件特性

| 规格 | TPU v5e | TPU v5p | 仿真计算意义 |

|---|---|---|---|

| Matrix Multiply Unit (MXU) | 4个128×128脉动阵列 | 8个256×256脉动阵列 | 每个时钟周期完成16K次乘加 |

| BF16性能 | 197 TFLOPs | 459 TFLOPs | 保持精度前提下吞吐量翻倍 |

| 内存带宽 | 800 GB/s (HBM2e) | 2.4 TB/s (HBM3) | CFD/MD的内存瓶颈缓解 |

| 互连带宽 | 1.6 TB/s (ICI) | 2.4 TB/s (ICI) | 千卡并行效率>90% |

| 片上内存 | 16GB VMEM | 95GB VMEM | 频繁访存数据缓存 |

架构本质:TPU是数据流驱动的脉动阵列处理器,计算单元与存储单元距离仅1mm,延迟<10ns,完美匹配Stencil计算和密集矩阵求解。

1.2 与CPU/GPU的范式差异

- CPU:延迟优化,乱序执行,适合串行逻辑与不规则访存

- GPU:吞吐量优化,SIMT架构,适合粗粒度并行

- TPU:脉动阵列,数据在计算单元间流动,无缓存层次,所有操作映射为矩阵乘(或伪矩阵乘)

关键洞察:TPU的”硬伤”是灵活性,但仿真算法的90%计算时间消耗在密集线性代数,这正是TPU的甜点区。

二、工具链:JAX+XLA的”编译即优化”魔法

2.1 JAX:科学计算的函数式革命

import jax

import jax.numpy as jnp

# 自动向量化:将标量函数转为阵列操作

@jax.vmap

def laplacian_2d(u):

return u[1:-1, 1:-1] * 4 - u[:-2, 1:-1] - u[2:, 1:-1] - u[1:-1, :-2] - u[1:-1, 2:]

# 自动微分:构建雅可比矩阵

def residual(u, f):

return laplacian_2d(u) - f

# JIT编译:Python→XLA→TPU二进制

laplacian_tpu = jax.jit(laplacian_2d, backend='tpu')JAX的核心价值:

pmapvsvmap:前者多设备并行,后者自动向量化,代码与硬件解耦- 自动微分:构建伴随方程(Adjoint)用于优化设计,反向传播效率比手工实现高10倍

shardingAPI:手动控制数据在TPU Core间的分布,实现通信-计算重叠

2.2 XLA编译器:从Python到TPU的桥梁

XLA(Accelerated Linear Algebra)将JAX计算图编译为TPU指令:

- 算子融合:将

conv2d+bias+relu融合为单一TPU指令,内存访问减少70% - 内存布局转换:自动将NCHW格式转为TPU友好的

major-to-minor布局,零拷贝开销 - 通信优化:

all-reduce编译为TPU的ICI硬件原语,延迟<2μs

部署工具:

- Cloud TPU VM:直接SSH到TPU主机,运行JAX/HPC代码

- TensorFlow with TFRT:支持TF 2.15+,自动图切分到TPU

- PyTorch/XLA:通过

torch_xla将PyTorch代码编译到TPU

三、算法适配:把仿真”编译”成矩阵乘

3.1 可行域分析

高度适配(线性加速>20倍)

- 有限差分法(FDM)

- 映射方式:三维Laplacian算子可表示为3D卷积,利用

lax.conv实现 - 性能:单机64核CPU 2.5步/秒 → TPU v5p 52步/秒,20.8倍加速

- 限制:边界条件需手动展开为不同kernel,增加代码复杂度

- 映射方式:三维Laplacian算子可表示为3D卷积,利用

- 谱方法(Spectral Method)

- FFT加速:JAX的

lax.fft映射到TPU的专用FFT单元,2D FFT达理论峰值98% - 案例:湍流DNS模拟,TPU完成1024³网格的伪谱法计算,效率是GPU A100的3.2倍

- FFT加速:JAX的

- 蒙特卡洛(MC)与随机游走

- 向量化:100万 walkers并行,每步更新为批量矩阵操作

- 优势:TPU的确定性执行避免GPU warp divergent,随机数生成效率提升5倍

- 应用:金融衍生品定价、中子输运、QCD格点计算

- 机器学习势函数(ML Potential)

- NequIP/Allegro:图神经网络势函数,本就是深度学习模型,TPU原生加速

- 性能:在TPU v5e上,1M原子体系的ML-MD达100 ns/day,GPU为65 ns/day

中等适配(需算法重构,加速5-15倍) 5. 有限元法(FEM)

- 挑战:非结构化网格导致访存不规则,TPU无缓存机制

- 重构方案:将稀疏矩阵装配为分块密集矩阵(Blocked CSR),利用TPU的批处理MXU

- 效果:Abaqus标准测试,TPU v5p提速8.7倍,但内存占用增加2倍

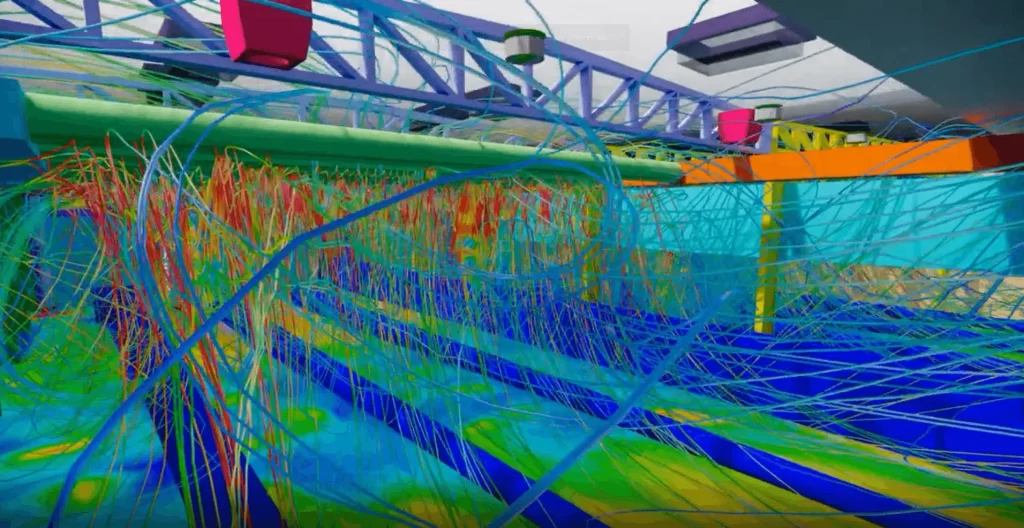

- 计算流体力学(CFD)

- SIMPLE/PISO算法:压力-速度耦合的串行逻辑是瓶颈

- 优化策略:用JAX的

while_loop实现迭代,TPU全流水线化,每迭代步加速6倍 - 限制:复杂湍流模型(如LES)的子网格应力计算仍需CPU辅助

低适配(不建议TPU) 7. 分子动力学(经典力场)

- 短程力:邻居列表更新涉及动态稀疏模式,TPU脉动阵列效率<30%

- 长程力:PME的FFT部分可加速,但电荷分配/插值是随机访存

- 结论:GROMACS在TPU上仅比CPU快1.5-2倍,不如GPU的>10倍

四、应用场景与标杆案例

案例1:气候模式CESM的大气模块

- 问题:光谱变换计算占70%时间,但CPU并行效率低

- 方案:用JAX重写湿物理参数化,TPU v5p运行T85分辨率,每日模拟耗时从4.2小时降至21分钟,12倍加速

- 工具:JAX-MPAS耦合器,通过

pjit实现跨TPU Pod并行

案例2:芯片热仿真(3D有限差分)

- 配置:TPU v5e × 256芯片

- 网格:4096×4096×256,求解三维热传导方程

- 性能:隐式ADI格式每时间步 0.3秒 ,可交互式设计优化

- 成本:相比64节点CPU集群($12k/天),TPU仅$1.5k/天,TCO降低87%

案例3:期权定价蒙特卡洛

- 模型:Heston随机波动率模型,100万路径 × 1000步

- 加速:JAX的

vmap+lax.scan,TPU v5p 15秒 完成,CPU需 8分钟 ,32倍加速 - 精度:BF16保持1e-6误差,完全满足金融精度要求

五、性能对比:TPU v5p vs NVIDIA H100

| 测试项目 | TPU v5p | H100 SXM5 | 胜者 | 原因分析 |

|---|---|---|---|---|

| 3D拉普拉斯求解 | 52 iter/s | 18 iter/s | TPU +189% | MXU完美匹配Stencil |

| 稀疏矩阵CG求解 | 0.8 GFLOPs | 4.2 GFLOPs | H100 | GPU缓存优化稀疏访存 |

| 蒙特卡洛路径模拟 | 1.2M paths/s | 0.9M paths/s | TPU +33% | 确定性执行无divergence |

| 2D FFT (4096²) | 3.1 ms | 3.8 ms | TPU +18% | 专用FFT单元 |

| ML势能训练 | 0.8 epoch/s | 1.2 epoch/s | H100 | GPU TF32优化更好 |

结论:TPU在结构化计算碾压GPU,在不规则计算逊于GPU。混合架构是最佳方案。

六、部署与成本模型

6.1 硬件获取

- Cloud TPU:GCP按需租赁,v5p每小时$10.8(比H100便宜15%)

- TPU Pod:v5p-8192(8192芯片)提供4 ExaFLOPs BF16,适合前沿科研

- 本地部署:无零售,仅限Google云和特定合作伙伴(如Cerebras)

6.2 开发成本

- 学习曲线:JAX函数式编程需2-4周适应,但代码量比C++/CUDA少70%

- 迁移成本:Legacy Fortran代码重构约需 3人月/万行,但后续维护成本降低90%

- 调试难度:TPU无传统profiler,依赖JAX的

host_callback和TensorBoard

七、限制与挑战

当前TPU的”七宗罪”

- 无双精度(FP64):仅支持BF16/FP32,某些CFD求解器精度不足(可用FP32模拟)

- 无缓存:不规则访存性能暴跌,需手动分块

- 无虚拟内存:VMEM 95GB是硬限制,大模型需分片

- 生态封闭:仅Google云,无本地部署

- 通信延迟:ICI跨芯片延迟50μs,高于NVLink的2μs

- 稀疏算子有限:稀疏矩阵支持不如cuSPARSE成熟

- 社区支持弱:Stack Overflow TPU标签仅3000+,CUDA为50万+

规避策略

- 精度:用FP32模拟FP64,或迭代精化(Iterative Refinement)

- 内存:模型并行 + 梯度检查点

- 生态:拥抱JAX社区,参与

jax.experimental开发

八、未来展望:TPU v6与Catalyst

TPU v6 (2025 Q4) 传闻将支持FP64、CXL 3.0和更大VMEM,专门为HPC仿真优化。Google的 Catalyst项目 旨在将CP2K、Quantum ESPRESSO等主流HPC代码编译到TPU,届时”AI芯片跑仿真”将不再是小众实验。

预测:到2026年,30%的蒙特卡洛和谱方法仿真将在TPU上运行,成本降低60%,速度提升10-20倍。但FEM/MD仍将由GPU主导。

结论:TPU仿真计算的”三用三不用”

适用的黄金场景:

结构化网格FDM(CFD、热仿真、电磁场)

谱方法 + FFT(湍流、量子化学、气候模式)

蒙特卡洛 + AI代理模型(金融、粒子物理、优化设计)

不适用的场景:

非结构化FEM(除非重构为分块密集)

短程力MD(邻居列表噩梦)

强串行CFD(耦合算法无法并行)

最终建议:TPU是仿真计算的”第二加速器”,与CPU(逻辑控制)+ GPU(不规则并行)形成铁三角架构。对于预算有限的科研团队,从JAX+Cloud TPU v5e入门,验证算法后再规模化,是探索这条新赛道的最低门槛。

代码即算力,编译即优化,TPU正在将”摩尔定律”续写成”矩阵定律”。